Silicon Valley Microelectronics は、ブロードバンド、Iライン、248nm、193nm、電子ビーム、ポジ、ネガ、ウェット、ドライレジストを含むフォトレジスト製品の包括的なリストを提供しています。SVMは、あらゆるウェハ径のパターニングとエッチングのためのフォトレジストソリューションを提供しています。プロジェクトの設計ルールは、特定のフォトレジストタイプ/性能を決定します。SVMは、CMOS、MEMS、TSV、FEOL、BEOLなどに関連するプロジェクトを扱っています。そのため、これらの用途やその他の用途に対応するフォトレジスト・タイプの豊富なラインナップを取り揃えています。SVMは、試験車アプリケーション用ウェハーのパターニング、エンジニアリングショートループフロー作業、犠牲保護層として使用するハードベークドブランケットPRの塗布、エッチングスタディなどの長い歴史を持っています。SVMは、さまざまな用途向けに、スピンまたはスプレーオンによるブランケットレジストを提供しています。特定のプロジェクトに関するご質問は、(408) 844-7100までご連絡いただくか、[email protected] まで電子メールでお問い合わせください。

利用可能なSVMフォトレジスト:

Iライン

I-Lineは、紫外光スペクトルの365nmに感度を持つ汎用レジストフィルムです。I-Lineフォトレジスト製品は、G線(435nm)とH線(405nm)に感光するブロードバンドレジストであることが多いですが、分光感度内で単色露光も可能です。このフィルムは、露光を正確に制御するための優れた密着性とめっき特性を持っており、MEMSやバンプなどのウェハレベルパッケージングプロセスでの使用に最適です。

193nm、248nm 深紫外線(DUV)

より高度なリソグラフィー用途向けに、SVMはDUV 248nm KrFおよび193nm ArFフォトレジスト製品を提供しています。製品は反射防止コーティングの有無にかかわらず塗布可能です。

厚膜フォトレジストとフォトイメージャブル・ポリイミド

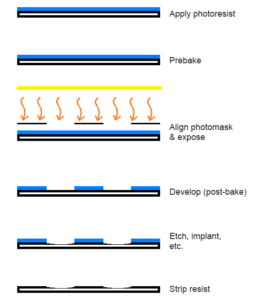

フォトレジストパターニングプロセス:

- 基板の準備 - 基板は洗浄され、脱水ベークを経て、残りの工程のためにウェハーを準備するために接着促進剤が添加されます。

- フォトレジストスピンコーティング - フォトレジストと溶剤の混合物から作られた薄く均一なコーティングは、スピンコーティングによって成膜されます。膜は、ウェハーを回転させながら(ダイナミックディスペンス)、または回転させずに(スタティックディスペンス)成膜されます。

- プリベーク – スピンコーティング後、フィルムの 20 ~ 40% はまだ溶剤が残っています。プリベークを追加すると、フォトレジストが乾燥し、フィルムが安定します。このステップにより、厚さが減り、フィルムの特性が変化し、接着性が向上し、粒子汚染の影響を受けにくくなります。

- 露光 - 光を当てることによってウェハーをパターン化するために、フィルムの溶解性を変化させます。露光には3つの形式があります:

- コンタクト - マスクがフォトレジストと接触しています。

- 近接性 - マスクはフォトレジストより約 15 ~ 20 μm 上にあります。

- 投影 - ミラーがマスクからウェハ表面に光のスリットを投影します。正しい露光を決定するために、エンジニアは光強度、スリットサイズ、基板のスピン速度を測定します。投影露光には2つのバージョンがあります:

- スキャン - コンピュータがウェーハ表面をスキャンし、ライトが移動して正しい領域を露光します。

- ステップアンドリピート - ウェハーの小さな領域が光にさらされます。

- Post-exposure bake – This step is generally for wafers with high resolution (<1 micron). In most other circumstances, the substrate goes straight from exposure to development.

- 現像 - ウェハーを化学洗浄し、マスクに残されたエッチングを露出させます。

- フォトレジストの剥離 - 化学的除去またはエッチングにより、ウェハ上の最終パターンを形成するために、残存するフォトレジストをすべて除去します。

ベイエリアなら4時間以内にどこでも。

米国では1日以内に発送されます。

国際的には3日以内に発送されます。